MCP CRI/CAST-32A is a position paper that provides a set of guidance for software planning and verification to embed multi-core chips in avionic platform. The position paper applies both for the multi-core processor hardware and the executive layer (e.g. RTOS, hypervisor) executed on top of the processor.

PHYLOG project has defined a set of assurance cases patterns dedicated to the MCP CRI/CAST-32A. The objectives were to:

- Translating abstruse and ambiguous textual standard requirements of the CAST-32A in more readable and understandable assurance case template libraries;

- Offering pre-defined templates for applicants that have been validated with certification authorities for the CAST-32A.

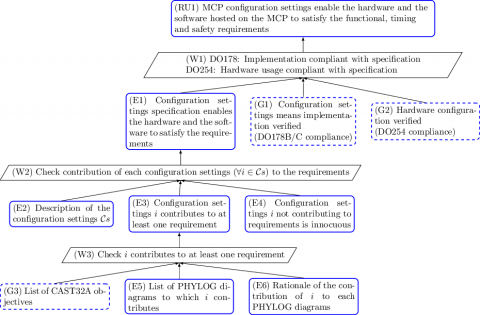

Φlog patterns for Resource Usage 1 (RU1)

Objective: The applicant has determined and documented the MCP configuration settings that will enable the hardware and the software hosted on the MCP to satisfy the functional, performance, timing and safety requirements of the system.

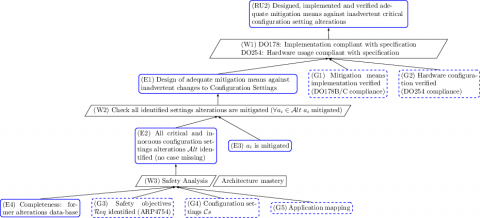

Φlog patterns for Resource Usage 2 (RU2)

Objective: The applicant has planned, developed, documented, and verified a means that ensures that in the event of any of the Critical Configuration Settings of the multi-core processor being inadvertently altered, an appropriate means of mitigation is specified.

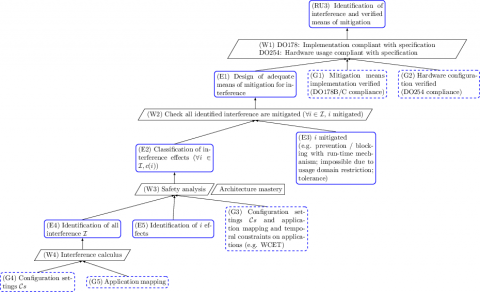

Φlog patterns for Resource Usage 3 (RU3)

Objective: The applicant has identified the interference channels that could permit interference to affect the software applications hosted on the multi-core processor cores, and has verified the applicant’s chosen means of mitigation of the interference.

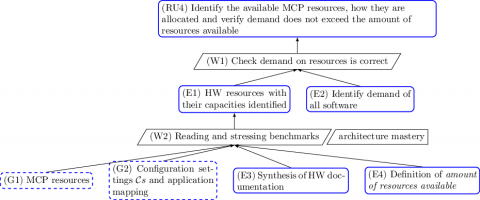

Φlog patterns for Resource Usage 4 (RU4)

Objective: The applicant has identified the available resources of the MCP and of its interconnect in the intended final configuration, has allocated the resources of the MCP to the software applications hosted on the MCP and has verified that the demands for the resources of the MCP and of the interconnect do not

exceed the available resources when all the hosted software is executing on the target processor.

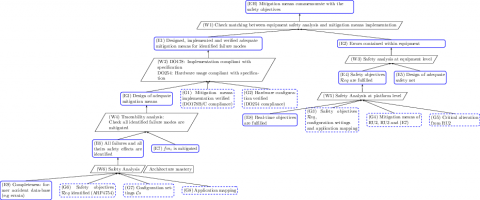

Φlog patterns for Error Handling (EH)

Objective: The applicant has identified the effects of failures that may occur within the multi-core processor and has planned, designed, implemented and verified means (which may include a safety net external to the multi-core processor) commensurate with the safety objectives, by which to detect and handle those failures in a fail-safe manner that contains the effects of any failures within the equipment in which the multi-core processor is installed.